## **CCD linear image sensors**

S13255-2048-02 S13256-2048-02

# Back-thinned CCD image sensors with electronic shutter function

The S13255-2048-02 and S13256-2048-02 are back-thinned CCD linear image sensors with an internal electronic shutter for spectrometers. These image sensors use a resistive gate structure that allows a high-speed transfer. Each pixel has a lengthwise size needed by spectrometers but ensures readout with low image lag. In addition, a TE-cooler is built into the package to keep the element temperature constant (about 5°C) during operation.

## 📮 Features

## Applications

- Built-in electronic shutter

- Minimum integration time: 2 μs

- High sensitivity from the ultraviolet region (spectral response range: 200 to 1100 nm)

- Readout speed: 10 MHz max.

- Image lag: 0.1% typ.

- Spectrometers

- Image readout

## Structure

| Parameter                                 | S13255-2048-02                                    | S13256-2048-02    |  |  |  |

|-------------------------------------------|---------------------------------------------------|-------------------|--|--|--|

| Pixel size (H $\times$ V)                 | 14 × 500 μm                                       | 14 × 1000 μm      |  |  |  |

| Number of total pixels ( $H \times V$ )   | 2128                                              | $3 \times 1$      |  |  |  |

| Number of effective pixels (H $\times$ V) | 2048                                              | $3 \times 1$      |  |  |  |

| Image size $(H \times V)$                 | 28.672 × 0.500 mm                                 | 28.672 × 1.000 mm |  |  |  |

| Horizontal clock phase                    | 2-pł                                              | nase              |  |  |  |

| Output circuit                            | Two-stage MOSFET source follower                  |                   |  |  |  |

| Package                                   | 28-pin ceramic DIP (refer to dimensional outline) |                   |  |  |  |

| Window                                    | Quartz glass*1                                    |                   |  |  |  |

| Cooling                                   | One-stage                                         | TE-cooled         |  |  |  |

\*1: Hermetic sealing

## **Resistive gate structure**

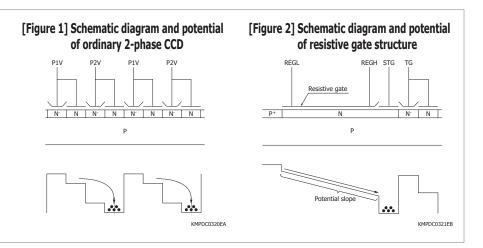

In ordinary CCDs, one pixel contains multiple electrodes and a signal charge is transferred by applying different clock pulses to those electrodes [Figure 1]. In resistive gate structures, a single high-resistance electrode is formed in the active area, and a signal charge is transferred by means of a potential slope that is created by applying different voltages across the electrode [Figure 2]. Compared to a CCD area image sensor which is used as a linear sensor by line binning, a one-dimensional CCD having a resistive gate structure in the active area offers higher speed transfer, allowing readout with low image lag even if the pixel height is large.

## Absolute maximum ratings (Ta=25 °C)

| Parameter                                  |      | Symbol          | Condition       | Min.               | Тур.               | Max.               | Unit |

|--------------------------------------------|------|-----------------|-----------------|--------------------|--------------------|--------------------|------|

| Operating temperature*2 *3                 |      | Topr            |                 | -50                | -                  | +60                | °C   |

| Storage temperature                        |      | Tstg            |                 | -50                | -                  | +70                | °C   |

| Output transistor drain voltage            |      | Vod             |                 | -0.5               | -                  | +25                | V    |

| Reset drain voltage                        |      | Vrd             |                 | -0.5               | -                  | +18                | V    |

| Output amplifier return voltage            |      | Vret            |                 | -0.5               | -                  | +18                | V    |

| All reset drain voltage                    |      | Vard            |                 | -0.5               | -                  | +18                | V    |

| Horizontal input source voltage            |      | VISH            |                 | -0.5               | -                  | +18                | V    |

| All reset gate voltage                     |      | VARG            |                 | -12                | -                  | +15                | V    |

| Storage gate voltage                       |      | Vstg            |                 | -12                | -                  | +15                | V    |

| Horizontal input gate voltage              |      | VIG1H, VIG2H    |                 | -12                | -                  | +15                | V    |

| Summing gate voltage                       |      | Vsg             |                 | -12                | -                  | +15                | V    |

| Output gate voltage                        |      | Vog             |                 | -12                | -                  | +15                | V    |

| Reset gate voltage                         |      | Vrg             |                 | -12                | -                  | +15                | V    |

| Transfer gate voltage                      |      | Vtg             |                 | -12                | -                  | +15                | V    |

| Resistive gate voltage                     | High | VREGH           |                 | -12                | _                  | +15                | V    |

| Low                                        |      | VREGL           |                 | -12                | -                  | +15                | v    |

| Horizontal shift register clock voltage    |      | Vp1h, Vp2h      |                 | -12                | -                  | +15                | V    |

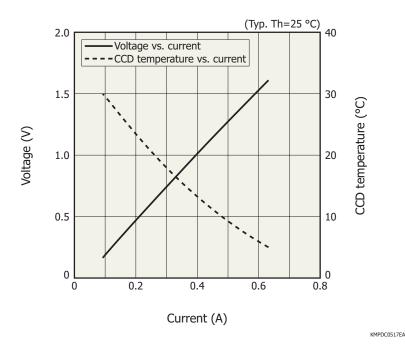

| Maximum current of built-in TE-cooler*4 *5 |      | Imax            | Tc*6=Th*7=25 °C | -                  | -                  | 1.8                | Α    |

| Maximum voltage of built-in TE-co          | Vmax | Tc*6=Th*7=25 °C | -               | -                  | 3.5                | V                  |      |

| Soldering conditions*8                     |      | Tsol            |                 | 260 °C, within 5 s | , at least 2 mm aw | ay from lead roots | -    |

\*2: Chip temperature

\*3: The sensor temperature may increase due to heating in high-speed operation. We recommend taking measures to dissipate heat as needed. For more details, refer to the technical information "Resistive gate type CCD linear image sensors with electronic shutter".

\*4: If the current greater than this value flows into the thermoelectric cooler, the heat absorption begins to decrease due to the Joule heat. It should be noted that this value is not the damage threshold value. To protect the thermoelectric cooler and maintain stable operation, the supply current should be less than 60% of this maximum current.

\*5: To ensure stable temperature control,  $\Delta T$  (temperature difference between Th and Tc) should be less than 30 °C. If  $\Delta T$  exceeds 30 °C, product characteristics may deteriorate. For example, the dark current uniformity may degrade.

\*6: Temperature of the cooling side of thermoelectric cooler

\*7: Temperature of the heat radiating side of thermoelectric cooler

\*8: Use a soldering iron.

Note: Exceeding the absolute maximum ratings even momentarily may cause a drop in product quality. Always be sure to use the product within the absolute maximum ratings.

## Operating conditions (Ta=25 °C)

| Parameter                       |                |                    | Symbol       | Min.  | Тур.         | Max. | Unit |  |

|---------------------------------|----------------|--------------------|--------------|-------|--------------|------|------|--|

| Output transistor drain voltage |                |                    | Vod          | 12    | 15           | 18   | V    |  |

| Reset drain voltage             |                |                    | Vrd          | 13    | 14           | 15   | V    |  |

| All reset drain voltage         |                |                    | Vard         | 13    | 14           | 15   | V    |  |

| All recet gate veltage          |                | High* <sup>9</sup> | VARGH        | 7     | 8            | 9    | V    |  |

| All reset gate voltage          |                | Low*10             | VARGL        | 0.5   | 1            | 2    | v    |  |

| Output gate voltage             |                |                    | Vog          | 2.5   | 3.5          | 4.5  | V    |  |

| Storage gate voltage            |                |                    | Vstg         | 2.5   | 3.5          | 4.5  | V    |  |

| Substrate voltage               |                |                    | Vss          | -     | 0            | -    | V    |  |

| Posistivo asto high volto       | 20             | High               | VREGHH       | 0.5   | 1            | 1.5  | v    |  |

| Resistive gate high voltage     | ye             | Low                | VREGHL       | -10.5 | -9.5         | -8.5 | V    |  |

| Resistive gate low voltag       | 0              | High               | Vreglh       | -     | VREGHH - 8.0 | -    | V    |  |

| Resistive gate low voltag       | e              | Low                | VREGLL       | -10.5 | -9.5         | -    | v    |  |

| Output amplifier return v       | oltage*11      |                    | Vret         | -     | 1            | 2    | V    |  |

| Tost point                      | Horizontal inp | ut source          | VISH         | -     | Vrd          | -    | V    |  |

| Test point                      | Horizontal inp | ut gate            | Vig1h, Vig2h | -10.5 | -9.5         | -    | V    |  |

| Harizantal chift register (     |                | High               | Vp1hh, Vp2hh | 5     | 6            | 8    | V    |  |

| Horizontal shift register of    | LIUCK VUILAYE  | Low                | Vp1hl, Vp2hl | -6    | -5           | -4   | v    |  |

| Summing gate veltage            |                | High               | VSGH         | 5     | 6            | 8    | v    |  |

| Summing gate voltage            |                | Low                | VSGL         | -6    | -5           | -4   | ]    |  |

| Posot gato voltago              |                | High               | Vrgh         | 7     | 8            | 9    | v    |  |

| Reset gate voltage              |                | Low                | Vrgl         | -6    | -5           | -4   |      |  |

| Transfor gata valtage           |                | High               | Vtgh         | 9.5   | 10.5         | 11.5 | v    |  |

| Transfer gate voltage           |                | Low                | Vtgl         | -6    | -5           | -4   | V N  |  |

| External load resistance        |                |                    | RL           | 2.0   | 2.2          | 2.4  | kΩ   |  |

\*9: All reset on

\*10: All reset off

\*11: Output amplifier return voltage is a positive voltage with respect to Substrate voltage, but the current flows in the direction of flow out of the sensor.

## Electrical characteristics [Ta=25 °C, fc=5 MHz, operating conditions: Typ., timing chart (P.6, 7)]

|                                          |                |            | -       | • • • • • |      |      |

|------------------------------------------|----------------|------------|---------|-----------|------|------|

| Parameter                                |                | Symbol     | Min.    | Тур.      | Max. | Unit |

| Signal output frequency                  |                | fc         | -       | 5         | 10   | MHz  |

| Line rate                                |                | LR         | -       | 2         | 4    | kHz  |

| Horizontal shift register cap            | bacitance      | Ср1н, Ср2н | -       | 200       | -    | pF   |

| All reset gate capacitance               |                | CARG       | -       | 100       | -    | pF   |

| Desistive gate epocitance                | S13255-2048-02 | Corc       | -       | 1000      | -    |      |

| Resistive gate capacitance               | S13256-2048-02 | CREG       | -       | 2000      | -    | – pF |

| Summing gate capacitance                 | ·              | Csg        | -       | 10        | -    | pF   |

| Reset gate capacitance                   |                | Crg        | -       | 10        | -    | pF   |

| Transfer gate capacitance                |                | Стд        | -       | 100       | -    | pF   |

| Charge transfer efficiency*1             | 2              | CTE        | 0.99995 | 0.99999   | -    | -    |

| DC output level                          |                | Vout       | 9       | 10        | 11   | V    |

| Output impedance                         |                | Zo         | -       | 300       | -    | Ω    |

| Output amplifier return cur              | rent           | Iret       | -       | 0.4       | -    | mA   |

|                                          | C122EE 2040 02 | PAMP*13    | -       | 75        | -    |      |

| Power consumption                        | S13255-2048-02 | PREG*14    | 50      | 100       | 160  |      |

|                                          | C122EC 2040 02 | PAMP*13    | -       | 75        | -    | – mW |

|                                          | S13256-2048-02 | PREG*14    | 30      | 60        | 90   |      |

| Resistive gate resistance*15             | S13255-2048-02 | Dara       | 0.4     | 0.7       | 1.4  | LO.  |

| Resistive gate resistance <sup>*13</sup> | S13256-2048-02 | RREG       | 0.7     | 1.1       | 2.2  | kΩ   |

\*12: Charge transfer efficiency per pixel of CCD shift register, measured at half of the full well capacity

\*13: Power consumption of the on-chip amplifier plus load resistance

\*14: Power consumption at REG

\*15: Resistance value between REGH and REGL

### Electrical and optical characteristics [Ta=25 °C, fc=5 MHz, operating conditions: Tvp. (P.3), timing chart (P.6, 7)]

| Dev                                | ramatar.                        | Cumbol | S13  | 255-2048                | 3-02 | S13  | 256-2048 | Linit |                          |  |

|------------------------------------|---------------------------------|--------|------|-------------------------|------|------|----------|-------|--------------------------|--|

| Pdi                                | rameter                         | Symbol | Min. | Тур.                    | Max. | Min. | Тур.     | Max.  | Unit                     |  |

| Saturation output voltage          |                                 | Vsat   | -    | Fw x CE                 | -    | -    | Fw x CE  | -     | V                        |  |

| Full well capacity*16              |                                 | Fw     | 150  | 200                     | -    | 150  | 200      | -     | ke⁻                      |  |

| Linearity error*17                 |                                 | LR     | -    | ±3                      | ±10  | -    | ±3       | ±10   | %                        |  |

| Conversion efficiency              |                                 | CE     | 9    | 10                      | 11   | 9    | 10       | 11    | µV/e⁻                    |  |

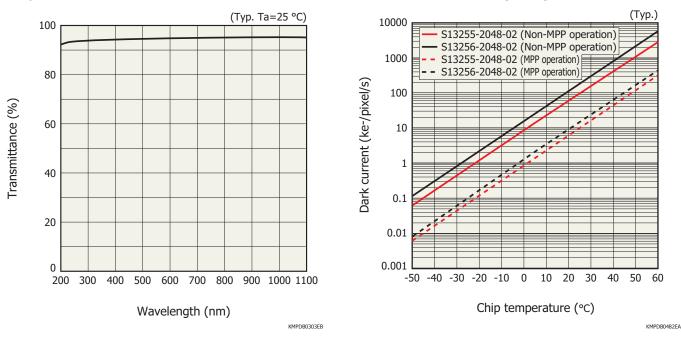

| Dark current*18                    | Non-MPP operation               | DS     | -    | 100                     | 300  | -    | 200      | 600   | ke <sup>-</sup> /pixel/s |  |

| Dark current*18                    | MPP operation                   | 05     | -    | 10                      | 40   | -    | 15       | 60    |                          |  |

| Dark output nonuniformity          | Non-MPP operation               | DCNUL  | -    | -                       | 300  | -    | -        | 300   | %                        |  |

|                                    | MPP operation                   | DSNU   | -    | -                       | -    | -    | -        | -     |                          |  |

| Readout noise                      |                                 | Nread  | -    | 30                      | 45   | -    | 30       | 45    | e⁻ rms                   |  |

| Dynamic range*19                   |                                 | Drange | -    | 6670                    | -    | -    | 6670     | -     | -                        |  |

| Defective pixels*20                |                                 | -      | -    | -                       | 0    | -    | -        | 0     | -                        |  |

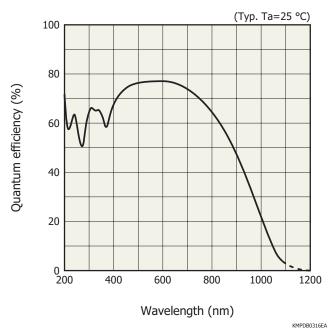

| Spectral response range            |                                 | λ      | 2    | 200 to 1100 200 to 1100 |      | 0    | nm       |       |                          |  |

| Peak sensitivity wavelength        |                                 | λр     | -    | 600                     | -    | -    | 600      | -     | nm                       |  |

| Photoresponse nonuniformity*21 *22 |                                 | PRNU   | -    | ±3                      | ±10  | -    | ±3       | ±10   | %                        |  |

|                                    | Average image lag of all pixels | I      | -    | 0.1                     | 1    | -    | 0.1      | 1     | %                        |  |

| Image lag*21 *23                   | Maximum image lag of all pixels | L      | -    | 1                       | 3    | -    | 1        | 3     | 70                       |  |

\*16: Operating voltages typ.

\*17: Signal level=1 ke<sup>-</sup> to 150 ke<sup>-</sup>. Defined so that the linearity error is zero when the signal level is at one-half the full well capacity.

\*18: Dark current is reduced to half for every 5 to 7 °C decrease in temperature.

\*19: Dynamic range (Drange) = Full well capacity / Readout noise

\*20: Pixels that exceed the DSNU or PRNU maximum

\*21: Measured at one-half of the saturation output (full well capacity) using LED light (peak emission wavelength: 660 nm)

\*22: Photoresponse nonuniformity =  $\frac{\text{Fixed pattern noise (peak to peak)}}{\text{Fixed pattern noise (peak to peak)}} \times 100 [\%]$

Signal

\*23: Percentage of unread signal level when a one-shot light pulse is irradiated so that the output is half the saturation output. The integration time during measurement is 5 μs for the S11155-2048-02 and 20 μs for the S11156-2048-02. For details, see the technical information (resistive gate type CCD linear image sensor with electronic shutter).

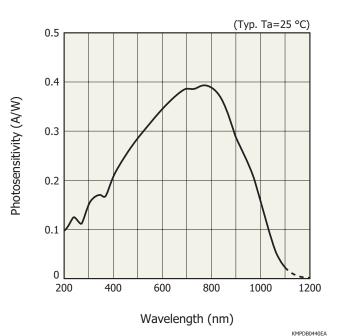

## Spectral response (without window)\*24

\*24: Spectral response with quartz glass is decreased according to the spectral transmittance characteristic of window material.

Dark current vs. chip temperature

### Spectral transmittance characteristic of window material

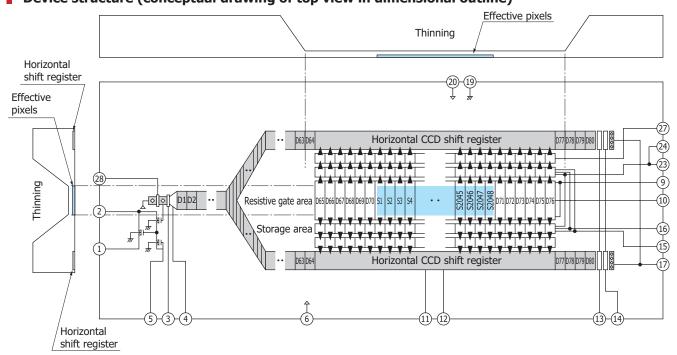

## Device structure (conceptual drawing of top view in dimensional outline)

Note: When viewed from the direction of the incident light, the horizontal shift register is covered with a thick silicon layer (dead layer). However, long-wavelength light passes through the silicon dead layer and may possibly be detected by the horizontal shift register. To prevent this, provide light shield on that area as needed. Note that the transmission of long wavelengths in the dead layer covering the horizontal shift register was reduced compared to previous products.

Signal charges that undergo photoelectric conversion at each pixel of the photosensitive area are directed upward or downward based on the boundary line at the center of the photosensitive area and transferred. Then, they are combined through the horizontal registers and read out by the amplifier.

KMPDC0609EA

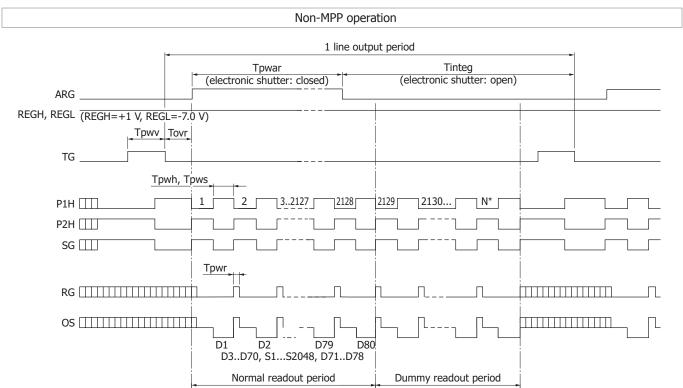

## Timing chart

$^{\ast}$  Apply clock pulses to the specified terminals during the period of dummy readout. Set the total number of clock pulses N, according to the integration time.

KMPDC0541EB

| Pai                     | Parameter           |              | Min. | Тур. | Max. | Unit |

|-------------------------|---------------------|--------------|------|------|------|------|

| ARG                     | Pulse width         | Tpwar        | 1    | -    | -    | μs   |

| AKG                     | Rise and fall times | Tprar, Tpfar | 200  | -    | -    | ns   |

| TC                      | Pulse width         | Tpwv         | 2    | -    | -    | μs   |

| TG                      | Rise and fall times | Tprv, Tpfv   | 20   | -    | -    | ns   |

|                         | Pulse width         | Tpwh         | 50   | 100  | -    | ns   |

| P1H, P2H* <sup>25</sup> | Rise and fall times | Tprh, Tpfh   | 10   | -    | -    | ns   |

|                         | Duty ratio          | -            | 40   | 50   | 60   | %    |

|                         | Pulse width         | Tpws         | 50   | 100  | -    | ns   |

| SG                      | Rise and fall times | Tprs, Tpfs   | 10   | -    | -    | ns   |

|                         | Duty ratio          | -            | 40   | 50   | 60   | %    |

| DC                      | Pulse width         | Tpwr         | 5    | 15   | -    | ns   |

| RG                      | Rise and fall times | Tprr, Tpfr   | 5    | -    | -    | ns   |

| TG - P1H                | Overlap time        | Tovr         | 1    | 2    | -    | μs   |

| Take question times     | S13255-2048-02      | Tinter       | 2    | 5    | -    |      |

| Integration time        | S13256-2048-02      | – Tinteg     | 2    | 20   | -    | μs   |

\*25: Symmetrical clock pulses should be overlapped at 50% of maximum pulse amplitude.

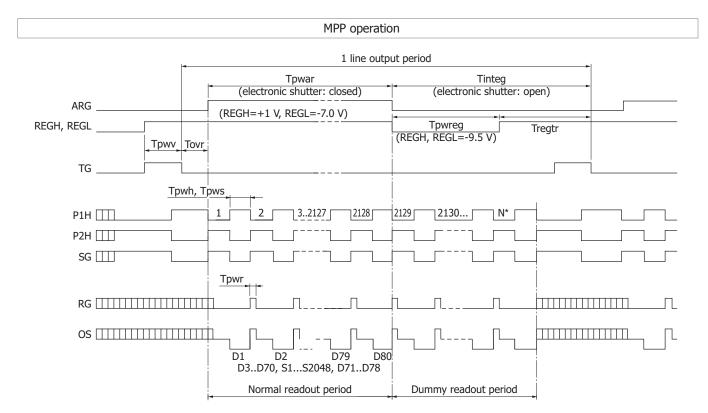

\* Apply clock pulses to the specified terminals during the period of dummy readout. Set the total number of clock pulses N, according to the integration time.

KMPDC0542EB

| Parameter               |                              | Symbol         | Min. | Тур.            | Max. | Unit |

|-------------------------|------------------------------|----------------|------|-----------------|------|------|

|                         | Pulse width                  | Tpwar          | *26  | -               | -    | μs   |

| ARG                     | Rise and fall times          | Tprar, Tpfar   | 200  | -               | -    | ns   |

|                         | Pulse width                  | Tpwreg         | -    | Tinteg - Tregtr | -    | μs   |

| REGH, REGL              | Rise and fall times          | Tprreg, Tpfreg | 100  | -               | -    | ns   |

| REGH, REGL              | Transfer time S13255-2048-02 | Troatr         | 2    | 5               | -    |      |

|                         | S13256-2048-02               | - Tregtr       | 2    | 20              | -    | μs   |

| TG                      | Pulse width                  | Tpwv           | 2    | -               | -    | μs   |

| IG                      | Rise and fall times          | Tprv, Tpfv     | 20   | -               | -    | ns   |

|                         | Pulse width                  | Tpwh           | 50   | 100             | -    | ns   |

| P1H, P2H* <sup>27</sup> | Rise and fall times          | Tprh, Tpfh     | 10   | -               | -    | ns   |

|                         | Duty ratio                   | -              | 40   | 50              | 60   | %    |

|                         | Pulse width                  | Tpws           | 50   | 100             | -    | ns   |

| SG                      | Rise and fall times          | Tprs, Tpfs     | 10   | -               | -    | ns   |

|                         | Duty ratio                   | -              | 40   | 50              | 60   | %    |

| RG                      | Pulse width                  | Tpwr           | 5    | 15              | -    | ns   |

| KG                      | Rise and fall times          | Tprr, Tpfr     | 5    | -               | -    | ns   |

| TG - P1H                | Overlap time                 | Tovr           | 1    | 2               | -    | μs   |

| Integration time        | S13255-2048-02               | Tintog         | 2    | 5               | -    |      |

| Integration time        | S13256-2048-02               | - Tinteg       | 2    | 20              | -    | μs   |

\*26: The Min. value of Tpwar is equal to the normal readout period.

\*27: Symmetrical clock pulses should be overlapped at 50% of maximum pulse amplitude.

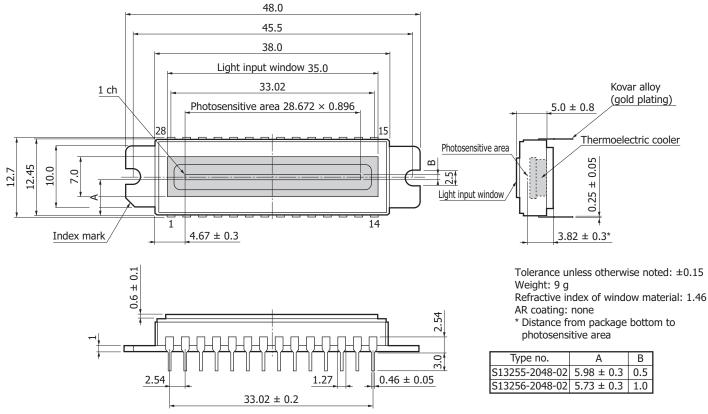

## Dimensional outline (unit: mm)

KMPDA0354EA

## Pin connections

| Pin no. | Symbol | Function                              | Remark (standard operation |

|---------|--------|---------------------------------------|----------------------------|

| 1       | OS     | Output transistor source              | RL=2.2 kΩ                  |

| 2       | OD     | Output transistor drain               | +15 V                      |

| 3       | OG     | Output gate                           | +3.5 V                     |

| 4       | SG     | Summing gate                          | Same pulse as P2H          |

| 5       | Vret   | Output amplifier return               | +1 V                       |

| 6       | RD     | Reset drain                           | +14 V                      |

| 7       | Th1    | Thermistor                            |                            |

| 8       | P-     | TE-cooler (-)                         |                            |

| 9       | REGL   | Resistive gate (low)                  | -7 V (non-MPP operation)   |

| 10      | REGH   | Resistive gate (high)                 | +1 V (non-MPP operation)   |

| 11      | P2H    | CCD horizontal shift register clock-2 | +6/-5 V                    |

| 12      | P1H    | CCD horizontal shift register clock-1 | +6/-5 V                    |

| 13      | IG2H   | Test point (horizontal input gate-2)  | -9.5 V                     |

| 14      | IG1H   | Test point (horizontal input gate-1)  | -9.5 V                     |

| 15      | ARG    | All reset gate                        | +8/+1 V                    |

| 16      | ARD    | All reset drain                       | +14 V                      |

| 17      | ISH    | Test point (horizontal input source)  | Connect to RD              |

| 18      | -      |                                       |                            |

| 19      | SS     | Substrate                             | GND                        |

| 20      | RD     | Reset drain                           | +14 V                      |

| 21      | P+     | TE-cooler (+)                         |                            |

| 22      | Th2    | Thermistor                            |                            |

| 23      | STG    | Storage gate                          | +3.5 V                     |

| 24      | STG    | Storage gate                          | +3.5 V                     |

| 25      | -      |                                       |                            |

| 26      | -      |                                       |                            |

| 27      | TG     | Transfer gate                         | +10.5/-5 V                 |

| 28      | RG     | Reset gate                            | +8/-5 V                    |

## HAMAMATSU

## Specifications of built-in TE-cooler (Typ., vacuum condition)

| Parameter                  | Symbol | Condition | Specification | Unit |

|----------------------------|--------|-----------|---------------|------|

| Internal resistance        | Rint   | Ta=25 °C  | 1.6           | Ω    |

| Maximum heat absorption*28 | Qmax   |           | 4.0           | W    |

\*28: This is a theoretical heat absorption level that offsets the temperature difference in the thermoelectric cooler when the maximum current is supplied to the unit.

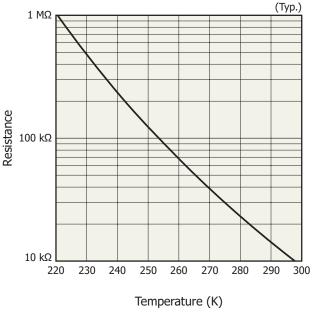

## Specifications of built-in temperature sensor

A thermistor chip is built in the same package with a CCD chip, and the CCD chip temperature can be monitored with it. A relation between the thermistor resistance and absolute temperature is expressed by the following equation.

$R_{T1} = R_{T2} \times exp B_{T1/T2} (1/T1 - 1/T2)$

RT1: Resistance at absolute temperature T1 [K] RT2: Resistance at absolute temperature T2 [K] BT1/T2: B constant [K]

The characteristics of the thermistor used are as follows. R298=10 k\Omega B298/323=3900 K

## Precautions

- · If the thermoelectric cooler does not radiate away sufficient heat, then the product temperature will rise and cause physical damage or deterioration to the product. Make sure there is sufficient heat dissipation during cooling. As a heat dissipation measure, we recommend applying a high heat-conductivity material (silicone grease, etc.) over the entire area between the product and the heatsink (metallic block, etc.), and screwing and securing the product to a heatsink.

- · Handle these sensors with bare hands or wearing cotton gloves. In addition, wear anti-static clothing or use a wrist band with an earth ring, in order to prevent electrostatic damage due to electrical charges from friction.

- · Avoid directly placing these sensors on a work-desk or work-bench that may carry an electrostatic charge.

- Provide ground lines or ground connection with the work-floor, work-desk and work-bench to allow static electricity to discharge.

- · Ground the tools used to handle these sensors, such as tweezers and soldering irons.

- · Long-term exposure to UV or X-ray irradiation will cause product characteristics to deteriorate. Avoid exposing the product to any unnecessary UV or X-ray irradiation.

It is not always necessary to provide all the electrostatic measures stated above. Implement these measures according to the amount of damage that occurs.

## Related information

www.hamamatsu.com/sp/ssd/doc\_en.html

- Precautions

- Disclaimer

- Image sensors

- Technical information

- · Resistive gate type CCD linear image sensors with electronic shutter

Information described in this material is current as of April 2019.

Product specifications are subject to change without prior notice due to improvements or other reasons. This document has been carefully prepared and the information contained is believed to be accurate. In rare cases, however, there may be inaccuracies such as text errors. Before using these products, always contact us for the delivery specification sheet to check the latest specifications.

The product warranty is valid for one year after delivery and is limited to product repair or replacement for defects discovered and reported to us within that one year period. However, even if within the warranty period we accept absolutely no liability for any loss caused by natural disasters or improper product use. Copying or reprinting the contents described in this material in whole or in part is prohibited without our prior permission.

## www.hamamatsu.com

#### HAMAMATSU PHOTONICS K.K., Solid State Division

1126-1 Ichino-cho, Higashi-ku, Hamamatsu City, 435-8558 Japan, Telephone: (81)53-434-3311, Fax: (81)53-434-5184

1120-1 ICHINO-CRO, HIgdShiFkU, HalmarhaltSU CUty, 453-6535 Japari, Telephone: (31)53-454-5311, F4X: (51)53-454-5184 U.S.A.: Hamamatsu Corporation: 360 Foothill Road, Bridgewater, N.J. 08807, U.S.A., Telephone: (1)908-231-1218, E-mail: usa@hamamatsu.com Germany: Hamamatsu Photonics Deutschland GmbH: Arzbergerstr. 10, D-82211 Herrsching am Ammersee, Germany, Telephone: (49)8152-375-0, Fax: (49)8152-265-8, E-mail: info@hamamatsu.de France: Hamamatsu Photonics France S.A.R.L: 19, Rue du Saule Trapu, Parc du Moulin de Massy, 9182 Massy Cedex, France, Telephone: (49)8152-375-0, Fax: (49)8152-265-8, E-mail: info@hamamatsu.de France: Hamamatsu Photonics France S.A.R.L: 19, Rue du Saule Trapu, Parc du Moulin de Massy, 9182 Massy Cedex, France, Telephone: (33)1 69 53 71 00, Fax: (33)1 69 53 71 10, E-mail: info@hamamatsu.fr United Kingdom: Hamamatsu Photonics Norden AB: Torshamnsgatan 35 16440 Kista, Sweden, Telephone: (46)8-509 031 00, Fax: (46)8-509 031 01, E-mail: info@hamamatsu.se Italy: Hamamatsu Photonics Italia S.r.l: Strada della Moia, 1 int. 6, 20020 Arese (Milano), Italy, Telephone: (46)8-509 031 00, Fax: (46)8-509 031 01, E-mail: info@hamamatsu.se Italy: Hamamatsu Photonics (China) Co., Ltd.: B1201, Jiaming Center, No.27 Dongsanhuan Beilu, Chaoyang District, 100020 Beijing, P.R.China, Telephone: (86)10-6586-6006, Fax: (86)10-6586-2866, E-mail: info@hamamatsu.co.m.tm Taiwan: Hamamatsu Photonics Taiwan Co., Ltd.: 8F-3, No. 158, Section2, Gongdao 5th Road, East District, Hsinchu, 300, Taiwan R.O.C. Telephone: (86)3-659-0080, Fax: (88)3-659-0081, E-mail: info@hamamatsu.co.m.tm